## **IIT Indore Patent Grant Press Note**

## **For Immediate Release:**

## Grant of Patent from Department of Electrical Engineering IIT Indore

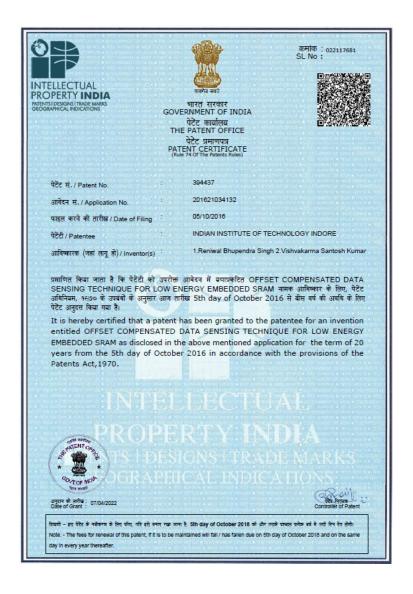

## **Patent Details**

**Indian Patent Application No.-** 201621034132

**Grant No.-** 394437

Filing Date- October 5, 2016 Date of Grant- April 7, 2022

**Title of the Patent-** OFFSET COMPENSATED DATA SENSING TECHNIQUE FOR LOW ENERGY EMBEDDED SRAM

Inventors- Bhupendra Singh Reniwal, Santosh Kumar Vishvakarma

**Contact Details**

Contact Person- Dr. Bhupendra Singh Reniwal and Dr. Santosh Kumar Vishvakarma

**Institution-** Indian Institute of Technology Indore

Email Address- skvishvakarma@iiti.ac.in

Website URL- <a href="http://ee.iiti.ac.in/">http://ee.iiti.ac.in/</a>

The IIT Indore granted a patent on "OFFSET COMPENSATED DATA SENSING TECHNIQUE FOR LOW ENERGY EMBEDDED SRAM" from the Patent Office, Government of India. These days, microprocessor-based hand-held devices are comprised of embedded memory which characterizes a huge share of the system-on-chip (SoC) and is susceptible to functional failure because of offset during chip fabrication. Considering this, the inventors Dr. Bhupendra Singh Reniwal and Prof. Santosh Kumar Vishvakarma from the Indian Institute of Technology Indore have developed a novel semiconductor memory architecture for low-energy electronics devices. The inventors developed a novel technique that can tolerate the variations in the modern IC fabrication process which lead to the failure of modern chips. This technique will enable the emerging chips to be fast enough in terms of reading the data from processor on-chip memory and will consume low energy. This will help to increase the accuracy, speed and consume low energy for data processing in Neuromorphic computing chips, low-energy wearable electronics devices, smartphones, personal healthcare assistants, and smart Cyber-Physical Systems applications

**Dr. Bhupendra** Singh Reniwal graduated from **SGSITS-Indore** and received Ph.D. from **IIT**, **Indore**. He has a mix of **industry and academic** experience both in India and abroad as a **Senior Product Development Engineer**, Semiconductor Vertical in **UST Global** Bangalore, Intel **Corporation Malaysia, and IBM Bangalore**. Where he was involved in developing Energy-Efficient Memory Architecture, I/O Circuit Design He has also served the, **BITS Pilani**, K. K. **Birla Goa** Campus as a faculty in the year 2017.

**Dr. Santosh Kumar Vishvakarma** is a Professor in the Department of Electrical Engineering, <u>Indian Institute of Technology Indore</u>, MP. He is engaged in teaching and research in the area of Energy-Efficient and Reliable SRAM Memory Design, Enhancing Performance and Configurable Architecture for DNN Accelerators, SRAM-based In-Memory Computing Architecture for Edge AI, Reliable, Secure Design for IoT Application, Design for Reliability. Dr. Vishvakarma obtained a Ph.D. degree on the topic from Microelectronics and VLSI Group, Department of Electronics and Computer Engineering, <u>Indian Institute of Technology</u>, <u>Roorkee (IITR)</u> in 2010.