## **Patent Summary**

The IIT Indore patent on "AN ULTRA LOW POWER, READ DECOUPLED-DIFFERENTIAL WRITE, 10T SRAM CELL WITH HIGHER READ/WRITE NOISE MARGIN" is granted by the Patent Office, Government of India. The inventors Dr. Vishal Sharma and Prof. Santosh Kumar Vishvakarma from the Indian Institute of Technology Indore have proposed the novel SRAM architecture for low power Industry application. The inventors breakthrough the power demand using a novel SRAM cell that works for low power subthreshold memory applications operating at ultra-low supply voltage. The architecture is more suitable for ultra-low-power battery-operated wearable electronic applications such as wireless sensors, mobile or any other handheld devices, and cache memory for processors/microcontrollers etc.

The design of SRAM memory cells has been very challenging with the continuous technology downscaling, and therefore the stability of SRAM gets vulnerable to the noise in VLSI circuit design. It is due to random variation at lower technology nodes through the process-variation and device-mismatch. Further, cache memory in SoC remains in standby mode and faces the burden of high leakage power consumption during subthreshold operation. To address these critical memory design issues, they have invented a novel 10T SRAM that reduces the leakage power using the subthreshold regime operation. The memory read speed and read/write stability have also been improved in this invented cell.

### For Immediate Release:

#### CONTACT:

Contact Person- Dr. Vishal Sharma, Dr. Santosh Kumar Vishvakarma Institution- Indian Institute of Technology Indore Email Address- skvishvakarma@iiti.ac.in Website URL- http://ee.iiti.ac.in/

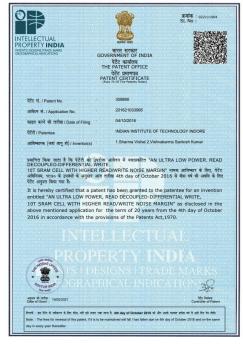

# Grant of Patent from Electrical Engineering Department, IIT Indore.

#### **Details:**

Indian Patent Application No.- 201621033995

Grant No.- 358866

Filing Date- October 4, 2016

Date of Grant- February 19, 2021

Title- AN ULTRA LOW POWER, READ DECOUPLED-DIFFERENTIAL WRITE, 10T SRAM CELL WITH HIGHER READ/WRITE NOISE MARGIN

Inventors- Vishal Sharma, Santosh Kumar Vishvakarma

The IIT Indore patent on "AN ULTRA LOW POWER, READ DECOUPLED-DIFFERENTIAL WRITE, 10T SRAM CELL WITH HIGHER READ/WRITE NOISE MARGIN" is granted by the Patent Office, Government of India. The inventors Dr. Vishal Sharma and Prof. Santosh Kumar Vishvakarma from the Indian Institute of Technology Indore have proposed the novel SRAM architecture for low power Industry application. The inventors breakthrough the power demand using a novel SRAM cell that works for low power subthreshold memory applications operating at ultra-low supply voltage. The architecture is more suitable for ultra-low-power battery-operated wearable electronic applications such as wireless sensors, mobile or any other handheld devices, and cache memory for processors/microcontrollers etc.

The design of SRAM memory cells has been very challenging with the continuous technology downscaling, and therefore the stability of SRAM gets vulnerable to the noise in VLSI circuit design. It is due to random variation at lower technology nodes through the process-variation and device-mismatch. Further, cache memory in SoC remains in standby mode and faces the burden of high leakage power consumption during subthreshold operation. To address these critical memory design issues, they have invented a novel 10T SRAM that reduces the leakage power using the subthreshold regime operation. The memory read speed and read/write stability have also been improved in this invented cell.

Dr. Vishal Sharma completed his Ph.D. from IIT Indore in 2019 and is currently pursuing his further research at Nanyang Technological University, Singapore as a Postdoctoral Research Fellow. His research interests include VLSI Compute In-memory design for Al applications, and High stability memory design for wearable electronic devices.

Professor Santosh Kumar Vishvakarma is currently working as an associate professor at the Indian Institute of Technology Indore. His current research interest is Compute-efficient, configurable VLSI circuit design for AI application, and low power and high-performance In-memory computing VLSI design.

Dr. Vishal Sharma

Dr. Santosh K Vishvakarma